Еще со времен первых систем Cray в суперкомпьютерах применяются векторные операции, а поддержка коротких векторов реализована уже и в ПК, что сегодня возможно благодаря применению в x86-процессорах Intel технологии AVX512, обеспечивающей работу с векторами длиной 512 бит (8 чисел с плавающей запятой двойной точности, DP). При поддержке распространенных в HPC-приложениях команд типа «умножить-и-сложить» каждое соответствующее исполнительное устройство в процессоре архитектуры Intel Skylake дает 16 DP-результатов за такт. Новые процессоры NEC SX-Aurora (SX-10+) поддерживают работу с более длинными векторами и с более расширенной функциональностью.

Процессоры SX-10+, именуемые в NEC также Vector Engine (VE), имеют 8 ядер, состоящих из скалярного и векторного блока. В каждом ядре содержится по 64 векторных регистра длиной по 256 DP-элементов, имеющих по 64-разряда. Соответственно, суммарная емкость регистров в каждом ядре составляет 128 Кбайт. В эти регистры помещаются исходные данные для выполнения векторных команд и результаты.

Ядра SX-10+ поддерживают выполнение векторных команд «умножить-и-сложить», для чего у них имеется по три устройства FMA (Floating Point Multiply Add) [1, 2], однако на каждом такте из векторных регистров в FMA поступает по 32 DP-элемента (е) векторов и формируется 32 DP-числа результата (рис. 1). Общая операция над 256 DP-элементами векторов завершается за 8 тактов. Таким образом, пиковая производительность ядра за такт составляет 32 x 2 x 3 = 192 FLOPS. Для сравнения, поддерживающие технологию AVX512 ядра процессоров Skylake дают за такт по 32 FLOPS, как и ядра процессоров-акселераторов KNL (Xeon Phi семейства x200 содержат до 72 ядер) [3], а в Tesla V100 используются 80 потоковых мультипроцессоров, содержащих по 32 DP-устройства (ядра), которые выдают по два результата, или 64 FLOPS за такт, для одного потокового мультипроцессора и, соответственно, 5120 FLOPS на весь V100.

.jpg) |

| Рис. 1. Операция «умножить-и-сложить» над векторными регистрами |

Производительность VE при работе с 32-разрядными числами одинарной точности вдвое выше, чем при работе с DP [1], однако большинство HPC-приложений работают с DP, поэтому далее все обсуждаемые результаты относятся именно к DP.

Кроме FMA-устройств, каждое ядро SX-10+ имеет устройство для выполнения деления и извлечения квадратного корня, дающих существенный вклад в полное время расчета (например, в приложениях молекулярной механики или молекулярной динамики), однако эти операции при расчете пиковой производительности не учитываются. Ядра VE содержат также устройства для выполнения операций над числами с фиксированной запятой и логических операций. Все эти устройства работают с векторными регистрами [2].

Очень важной для обеспечения эффективной работы с векторами является поддержка пошаговой загрузки векторных регистров из памяти и соответствующей записи из них в память. Кроме того, в SX-Aurora имеются еще и более сложные команды сборки/разборки векторных регистров с непрямым доступом к памяти типа работы с элементами массивов, имеющих двухуровневую индексацию a (index (i)), в синтаксисе языка Fortran. Эти команды поддерживались и в предыдущем поколении векторных процессоров NEC SX-ACE.

Другой кардинально важный для обеспечения высокой производительности компонент архитектуры VE — подсистема памяти. В VE применяется стандарт памяти с высокой пропускной способностью — High Bandwidth Memory (HBM2), трехмерная память стековой организации, интегрированная с процессором на кристалле посредством соединительной подложки (технология «silicon interposer»). Кроме NEC, созданием подложки для VE занимались также компании TSMC и Broadcom. Эта память состоит из блоков, содержащих 4 или 8 «матриц» емкостью по 1 Гбайт, а всего VE имеет шесть блоков HBM2 (рис. 2). Таким образом, общая емкость HBM2 в VE составляет 24 или 48 Гбайт. Канал доступа к каждому блоку имеет пропускную способность 200 Гбайт/с, что дает 1,2 Тбайт/с общей производительности памяти для VE. Для сравнения, в KNL ускоренная память MCDRAM имеет емкость 16 Гбайт при 490 Гбайт/с, а в V100 применяется HBM2 емкостью 16 Гбайт с 900 Гбайт/с, что свидетельствует о преимуществах SX-Aurora.

.jpg) |

| Рис.2. Общее строение VE в NEC SX-Aurora |

Важнейшая особенность SX-Aurora, обеспечивающая высокую эффективность работы с памятью, — «интерфейс» между HBM2 и ядрами, представляющий собой общий для них программно управляемый кэш LLC (Last Level Cache). Гранулярность записи данных в LLC cоставляет 8 байт, а гранулярность по доступу к памяти в SX-10+ — 128 байт. Кэш имеет емкость 16 Мбайт (по 2 Мбайт на ядро) и состоит из двух частей по 8 Мбайт (рис. 2). Пропускная способность канала от ядра к кэшу составляет 384 Гбайт/с, а от ядра к памяти — 153,6 Гбайт/с при общей пропускной способности памяти LLC около 3 Тбайт/с. Для связи между двумя частями LLC, как и для связи между ядрами, используется «межсоединение» 2D mesh, концептуально аналогичное применяемому в KNL и Skylake. В LLC поддерживается технология обратной записи, что обеспечивает когерентность кэша и возможность применения традиционного для систем с общей памятью распараллеливания программ посредством OpenMP [1, 2].

Процессоры SX-Aurora — это развитие векторных процессоров NEC SX-ACE, в которых также поддерживались механизмы работы с памятью, обеспечивающие внеочередной доступ: программно управляемый буфер ADB (Assignable Data Buffer) и специальные регистры MSHR (Miss Status Handling Registers) [4]. В SX-Aurora буфер ADB входит в LLC.

Емкость LLC можно сопоставить с емкостью кэшей старшего уровня в процессорах Intel KNL (кэш L2 в моделях Xeon Phi x200 имеет емкость по 0,5 Мбайт на ядро и максимальную емкость 36 Мбайт). Такие же показатели имеет кэш L2 в Xeon Phi архитектуры Knights Mill (модели x205). В серверных процессорах Skylake — Xeon Scalable Processor, в классе Gold емкость кэша L3 в расчете на ядро также существенно ниже, чем у SX-10+, — 1,375 Мбайт. Соответственно, у старших 20-ядерных моделей Intel Xeon 6154 этого класса общая емкость L3 равна 24,75 Мбайт.

Важная особенность вычислительных систем NEC TSUBASA — гибридная архитектура. Эти системы представляют собой серверы под управлением ОС Linux, а процессоры SX-Aurora служат к ним дополнением, однако, в отличие от акселераторов, включая и GPU, приложения выполняются на SX-Aurora полностью, а не отдельными частями. Например, на GPU от Nvidia выполняются только те части приложения, где может быть обеспечена высокая производительность с плавающей запятой, а другие части выполняются на сервере-хосте стандартной архитектуры, тогда как в SX-Aurora приложение выполняется целиком, включая операции ввода-вывода. Запрос на ввод-вывод передается от VE к серверу-хосту стандартной архитектуры, для которого в NEC используется термин Vector Host (VH). VE работает с VH через шину PCIe 3.0 x16, которая применяется и для коммуникаций VE между собой [2].

В реализации NEC SX-10+ применена технология 16 нм FinFET (Fin Field Effect Transistor — «техпроцесс с вертикально расположенным затвором»), что позволило сделать процессор компактным — его размеры всего 33 x 14,96 мм против 76,0 x 56,5 мм у 20-ядерного процессора Xeon Gold 6148. У Nvidia V100 площадь — 815 кв. мм.

Производитель предлагает три модели процессоров SX-10+: 10A, 10B и 10С, отличающихся емкостью памяти HBM2 и тактовыми частотами 1,4 или 1,6 ГГц. Это близко к применяемым в KNL — 1,3–1,5 ГГц, однако для процессоров Intel тактовая частота при работе с технологией AVX (и, соответственно, при подсчете пиковой производительности) ниже, чем базовая. Hапример, у KNL она ниже базовой на 200 МГц, а для Xeon Gold 6148 при базовой частоте 2,4 ГГц частота для AVX512 составляет 1,6 ГГц. Тактовая частота NEC 10A равна 1,6 ГГц, чему соответствует пиковая производительность одного ядра 307,2 GFLOPS, а всего процессора 10A — 2,45 TFLOPS. Для сравнения, максимальная пиковая производительность KNL близка к 3 TFLOPS, а V100 при увеличенной частоте 1,53 ГГц — 7,8 TFLOPS. Модель 10B отличается от 10A только тактовой частотой в 1,4 ГГц, а 10С от 10B — уменьшенной с 48 до 24 Гбайт емкостью HBM2.

Средняя пропускная способность работы с памятью каждого ядра 10A и 10B составляет 150 Гбайт/с против 94 Гбайт/с в 10C, а всего процессора — 1,2 Тбайт/с и 0,75 Тбайт/с соответственно. Потребляемая мощность платы SX-Aurora TSUBASA не превышает 300 Вт против 150 Вт для TDP одного процессора Xeon Gold 6148 и 260 Вт у Xeon Phi 7290F. Процессоры 10A предполагают работу только с водяным охлаждением, 10B — еще и с воздушным, а 10С — только с воздушным; для него VE имеет специальную плату.

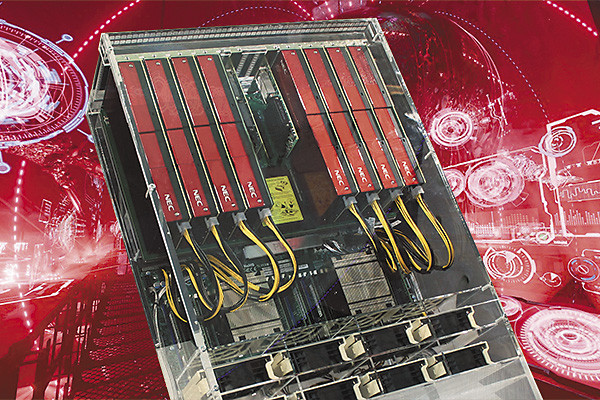

Диапазон систем TSUBASA простирается от рабочих станций A100 до стоечных суперкомпьютеров A500 (см. таблицу).

Модели TSUBASA, кроме типа и количества используемых VE, отличаются также разными VH. Во всех VH в качестве x86-процессоров используются Intel Xeon микроархитектуры Skylake, входящие в семейства Silver 4100 или Gold 6100 с памятью DDR4/2666 МГц. Так, в A100-1 и A300-2 доступно максимум по 6 DIMM общей емкостью 192 Гбайт, а в A300-4 и A300-8 доступно вдвое больше памяти. Старшая модель A500-64, которую NEC относит к суперкомпьютерам, представляет собой стойку, содержащую до 64 VE и 8 VH. С применением процессоров 10A эта модель достигает максимальной пиковой производительности 157,3 TFLOPS. С учетом энергопотребления A500-64 в 30 кВт, понятно, что на его основе можно легко построить суперкомпьютерный кластер петафлопсной производительности.

Для построения кластеров, системы TSUBASA обеспечивают работу со 100-гигабитным межсоединением Infiniband EDR 4x.

В качестве базовой операционной системы для VH используется дистрибутив RHEL 7.3, а на VE работает своя ОС, минимизирующая взаимодействие с ядром Linux для снижения накладных расходов. Поскольку приложения полностью выполняются на VE, их можно транслировать с оптимизирующими под SX-10+ компиляторами от NEC, поддерживающими языки программирования Fortran 2003 (c расширениями от Fortran 2008), Cи 11 и C++ 14. Эти компиляторы обеспечивают векторизацию и автоматическое распараллеливание. Наряду с этим предоставляются средства OpenMP 4.5 и MPI 3.1, а также оптимизированные математические библиотеки [1, 2]. Важно, что MPI-операции выполняются напрямую между VE через PCIe, без обращения к VH. Кроме того, NEC предлагает собственную систему пакетных очередей NQSV, распределенную параллельную файловую систему ScaTeFS и др.

Преимущества NEC SX-Aurora (высокая производительность с плавающей запятой при низком энергопотреблении и отличные характеристики используемой памяти) еще нужно научиться использовать при работе с реальными приложениями — на данный момент единственные доступные показатели реальной производительности приводятся в [1] и относятся к стандартным тестам памяти STREAM/triad и тесту HPL. Результаты работы на процессоре 10B сопоставлены с данными для Nvidia Tesla V100, Intel KNL и Xeon Skylake (двухпроцессорная система с Xeon Gold 6148 (SKL)). На тесте STREAM пропускная способность памяти у VE почти в пять раз выше, чем у SKL, и существенно выше по сравнению и с KNL, и с V100. А на тесте HPL процессор VE показал производительность, близкую к SKL, но лучше, чем у KNL. Однако наивысшие результаты теста HPL достигнуты на V100: вдвое выше, чем у VE. По отношению пропускной способности памяти к стоимости процессор NEC VE в пять раз превосходит Intel SKL и также кардинально лучше, чем KNL и V100. А по отношению HPL-производительности к стоимости VE близок к SKL и превосходит KNL, однако этот показатель у V100 лучше, чем у VE.

По производительности на тесте HPL процессоры VE и Intel SKL демонстрируют близкие результаты, включая и данные по отношению производительность/стоимость, что позволяет сделать вывод и о сравнимой стоимости (можно оценить процессор 10B на уровне 6 тыс. долл., однако прямых указаний по стоимости аппаратных средств c SX-Aurora производитель не приводит).

***

Процессоры NEC SX-10+ — это потенциальная альтернатива GPU, особенно на фоне недавнего объявления Intel о прекращении развития линии процессоров Xeon Phi KNL. Однако полноценной заменой KNL процессоры VE считать нельзя — они работают только в гибридных вычислительных системах, включающих x86-процессоры. Вместе с тем высокие характеристики пропускной способности памяти расширяют потенциальные сферы применения TSUBASA — кроме HPC-приложений, компания NEC указывает и на такие области, как обработка больших данных, задачи искусственного интеллекта, включая и задачи машинного обучения. При разработке приложений автоматическая векторизация в компиляторах NEC проще, чем распараллеливание вручную, однако работа с длинными векторами может оказаться не так эффективна. Компания NEC активизировала работы по развитию программного инструментария для разработки приложений, например для операций с разреженными матрицами, что актуально не только для машинного обучения, но и, например, для классических для HPC-задач квантовой химии.

Литература

- Momose S. SX-Aurora TSUBASA. Brand-new Vector Supercomputer, SC’17 Supercomputer Forum (2017).

- URL: http://www.nec.com/en/global/solutions/hpc/sx/vector_engine.html (дата обращения: 18.03.2018).

- М. Кузьминский. Из ускорителей в процессоры // Открытые системы.СУБД.— 2016.— № 3. — C. 4–6. URL: https://www.osp.ru/os/2016/03/13050252 (дата обращения: 18.03.2018).

- Ryusuke Egawa e.a. Early Evaluation of the SX-ACE Processor (2014). URL: http://sc14.supercomputing.org/sites/all/themes/sc14/files/archive/tech_poster/ poster_files/post196s2-file3.pdf (дата обращения: 18.03.2018).

Михаил Кузьминский (kus@free.net) — старший научный сотрудник, Институт органической химии РАН (Москва).

.jpg)