Корпорация IBM создала мэйнфреймы, ставшие наиболее распространенными для своего времени универсальными компьютерами, затем предложила массовый персональный компьютер, а теперь разработала RISC-процессор Power9, претендующий на роль ведущего обработчика больших данных. SPARC64 и архитектура Power — единственные сегодня действующие представители RISC-архитектуры высокой производительности.

В основной статье IBM разработчики отмечают четыре области применения Power9 [1]:

- прогнозная аналитика, искусственный интеллект и когнитивные вычисления;

- облачные и гипермасштабируемые центры обработки данных;

- корпоративные вычисления;

- высокопроизводительные вычисления (High Performance Computing, HPC).

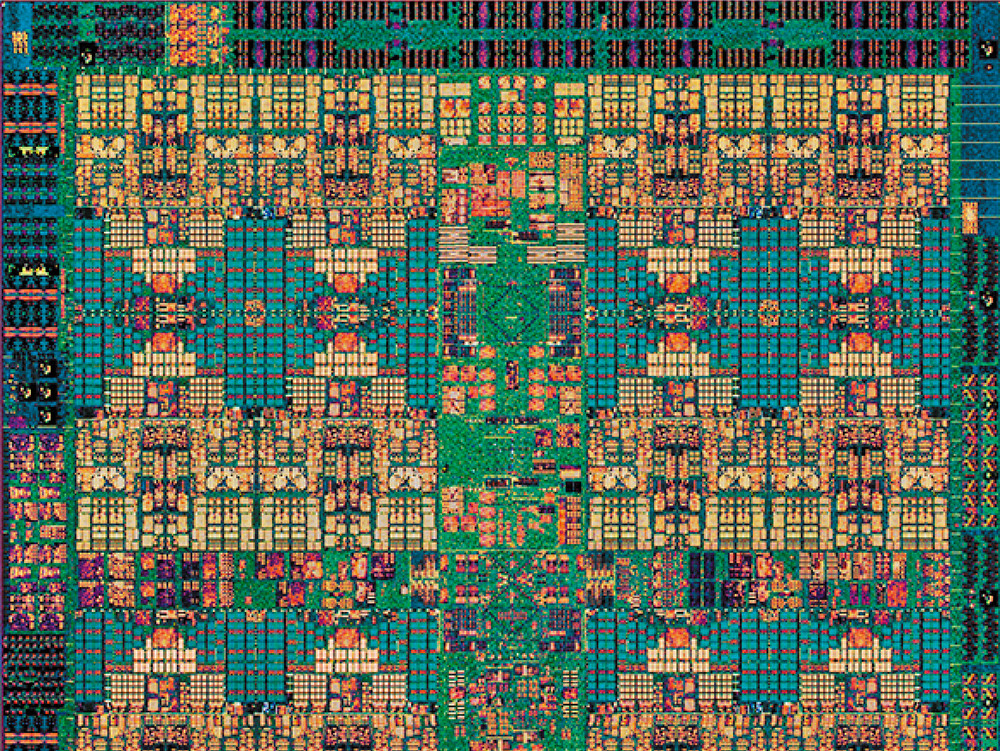

Естественно, в первую очередь речь идет именно о быстроразвивающейся области обработки больших данных, а в сфере HPC позиции Power9 достаточно сильны благодаря эффективному подсоединению графических процессоров (GPU) и высокой пропускной способности памяти. Наибольшего внимания заслуживают новые возможности Power9, которые будут востребованы в когнитивной эре. Конечно, много компонентов микроархитектуры Power9 было взято из Power8 [2], однако в новом процессоре имеется ряд оригинальных решений, даже на базовом уровне позволяющих говорить о значительном прогрессе относительно предшественника. Power9 производят по 14-нанометровой технологии Fin-FET (транзисторы с трехмерными затворами), а процессор содержит 8 млрд транзисторов на площади 695 кв. мм (https://en.wikichip.org/wiki/ibm/microarchitectures/power9), что чуть больше, чем в Power8.

Структура конвейеров разделяется на фронтальный компонент (внешний, до начала выполнения команд отвечающий, например, за диспетчирование) и компонент блоков выполнения (EU). Усовершенствованы были оба компонента. В частности, существенно улучшено предсказание переходов для внеочередного выполнения команд, а архитектура EU претерпела значительные изменения.

На одном уровне EU, называемом Slice (S), содержатся векторно-скалярные устройства (Vector and Scalar Unit,VSU), работающие с 64-разрядными данными — как целочисленными, так и в формате с плавающей запятой (рис. 1). Кроме того, здесь имеются традиционные блоки загрузки/записи данных (Load Store Unit, LSU), обрабатывающие до четырех операций чтения/записи двойных слов за такт, устройство выполнения переходов (Branch Unit, BRU) и устройство выборки команд (Instruction Fetch Unit, IFU), способное выбирать восемь команд за такт в буфер команд и содержащее оптимизированный предсказатель переходов для поддержки внеочередного выполнения команд. В общем конвейере VSU выполняются не только целочисленные операции и операции с плавающей запятой, но также и криптографические команды [1].

_450.png) |

| Рис. 1. Архитектура ядра SMT4 |

Из двух S образуется суперслой (SS), работающий со 128-разрядными данными (в том числе с числами нового типа — например, 128-разрядными числами с плавающей запятой четверной точности). Процессорное ядро Power9 типа SMT4 (аппаратная поддержка четырех программных нитей, Simultaneous MultiThreading 4) основывается на двух SS и содержит еще и традиционные блоки (рис. 1). Но Power9 может базироваться и на ядрах других типов — SMT8, которые вдвое больше по размерам, чем SMT4, и включают четыре 128-разрядных SS плюс те же увеличенного размера традиционные блоки. Общее число процессорных ядер SMT4 в микросхеме Power9 равно 24, а в варианте с SMT8 — 12. (Основа ядра на рис. 1 заключена в cинюю рамку, а в ядре SMT8 будет вдвое больше всех компонентов). SMT-ядра поддерживают внеочередное выполнение команд; SMT4 обеспечивает возможность завершения до 128 команд на каждом такте, а SMT8 — до 256 команд.

Процессор Power9 c 24 SMT4-ядрами предназначен для универсального применения в качестве платформы для ОС Linux, 12-ядерный Power9 на SMT8 ориентируется на работу систем c виртуализацией через PowerVM для Linux и ОС IBM i и AIX. В версии ядра Linux 4.12 уже имеется расширенная поддержка Power9.

Для областей приложений Power9 особенно важна иерархия системы памяти. Кэш команд — 8-канальный, емкостью 32 Кбайт. Для SMT4 имеется личный (локальный) 8-канальный наборно-ассоциативный кэш данных первого уровня (L1) емкостью 32 Кбайт. Также 8-канальный наборно-ассоциативный кэш второго уровня (L2) емкостью 512 Кбайт на ядро SMT8 является общим для двух входящих в SMT8 ядер SMT4. Внешний кэш третьего уровня (L3) имеет архитектуру NUCA с неоднородным доступом и построен на технологии eDRAM (как и в Power8). Емкость его области на одном ядре SMT8 (общая для двух ядер SMT4) cоставляет 10 Мбайт, а сам кэш — 20-канальный наборно-ассоциативный. Соответственно, для 12 областей на 12 ядрах SMT8 в Power9 емкость общего кэша L3 составляет 120 Мбайт. Для образования общего кэша L3 обмен данными между его областями реализуется через общий высокопроизводительный коммутатор. Организация работы кэш-памяти в Power9 также была улучшена.

Что касается собственно оперативной памяти для работы Power9, то она основана на технологии DDR4, однако имеются две разные группы вычислительных SMP-систем, которые будут строиться на базе Power9, — c «горизонтальным» и «вертикальным» масштабированием. Речь идет об одно-, двух- или многопроцессорных SMP-системах. В первой группе память построена с обычным прямым подсоединением через восемь портов (два блока по четыре порта) DDR4 с общей пропускной способностью 120 Гбайт/с. Каждая операция чтения может охватывать 64 или 128 байт. Максимальная емкость памяти на один процессорный разъем (сокет) составляет 4 Тбайт, а доступ ко всей памяти реализуется через общий коммутатор.

Для многопроцессорных SMP-систем на базе Power9 работа с памятью будет организована по-другому — с использованием буферной архитектуры памяти из Power8. Буферы памяти располагаются на специальной микросхеме Centaur, которая для Power8 работала с памятью DDR3, а теперь — с DDR4. На каждый сокет можно подсоединить 8 Тбайт, и имеется восемь буферных каналов памяти с общей пропускной способностью 230 Гбайт/с. Например, на базе четырех четырехпроцессорных систем можно построить общую SMP-систему на 16 процессоров, связываемых между собой по топологии, которая требует не более двух прыжков между самыми удаленными Power9 [3]. Надо также отметить, что и для обмена информацией между процессорами SMP-систем используется общий коммутатор (рис. 2).

_500.png) |

| Рис. 2. Общая архитектура Power9 |

Важнейшая оригинальная особенность архитектуры Power9 — межсоединения и соответствующие интерфейсы. В Power9 имеется два коммутаторных межсоединения: для команд и данных. Коммутатор для данных имеет структуру, основанную на 96 элементах, образующих двумерную топологию 9x12. Каждый элемент работает на частоте 2,4 ГГц и передает 32 байта за такт, что дает 76,8 Гбайт/с. А суммарная пропускная способность составляет около 7 Тбайт/с. Такой коммутатор применяется для локальных SMP-обменов данными между ядрами Power9 (включая поддержку когерентности кэша L3) и для доступа от процессора к целому ряду разных внешних по отношению к Power9 устройств: к другим Power9 в SMP-системах; к акселераторам, включая CAPI (Coherent Accelerator Processor Interface) 2.0 и OpenCAPI для подключения ускорителей FPGA и заказных интегральных схем (ASIC), к GPU Nvidia по каналу NVLink 2.0; к оперативной памяти; к внешним устройствам через 48 линий PCIe v4 (рис. 2). Аппаратная поддержка подсоединения разных акселераторов показывает нацеленность Power9 на построение гетерогенных систем с увеличенной производительностью.

Каждый канал, подсоединяемый к коммутатору от кэша L3 ядра SMT8 для обеспечения когерентности имеет пропускную способность 128 Гбайт/с в каждом направлении (таких каналов 12). Работающий через коммутатор локальный SMP-интерфейс для обмена данными между четырьмя сокетами, расположенными на материнской плате, использует 30 линий по 16 Гбит/с. Материнские платы можно соединить между собой кабелями для построения многопроцессорных SMP-систем, содержащих до 16 сокетов. Для каждого такого соединения используются 20 межпроцессорных линий с пропускной способностью по 25 Гбит/с, работающих через общий коммутатор. Через коммутатор работает интерфейс доступа к NVLink и новому варианту CAPI, который базируется на 48 линиях BlueLink с 25 Гбит/с, что дает суммарную дуплексную пропускную способность 300 Гбайт/с. Интерфейс OpenCAPI задействует восемь таких линий. Все эти линии могут использоваться и как межпроцессорные. Ввод-вывод через PCIe обеспечивается на суммарной дуплексной пропускной способности 190 Гбайт/с (через шины PCIe подсоединяются FPGA-ускорители CAPI 2.0).

Отдельного внимания заслуживает поддерживаемая в Power9 расширенная система команд ISA v3.0, специально предназначенная для работы в том числе с такими прикладными областями, как прогнозная аналитика, искусственный интеллект и когнитивные вычисления. Поддерживаются новые типы данных, например 128-разрядные числа с плавающей запятой четверной точности (IEEE 754-2008), используемые в финансовых приложениях и в сфере безопасности, а также целые, применимые в базах данных.

Система команд процессора Power и ранее содержала оригинальные команды, например криптографические, а в версии 3.0 появилась команда генерации случайного числа, сертифицированная NIST. Кроме того, у Power9 имеются атомарные команды для работы с памятью, выполняемые контроллером памяти: сравнение, нахождение максимума и минимума и др.

Что касается команд с плавающей запятой, то, кроме операций умножения и сложения, в Power9 поддерживаются деление и извлечение квадратного корня. Для наиболее традиционной в области HPC работы с числами двойной точности (DP) каждая SS может завершать за такт две скалярные или одну векторную (длиной в два числа) операцию типа «умножить и сложить», то есть можно получать четыре DP-результата за такт. Cоответственно, типовое для HPC ядро SMT4 с двумя SS дает восемь DP-результатов за такт, а весь Power9 — 192 результата. (Пиковую DP-производительность Power9 в GFLOPS можно получить, умножив этот показатель на тактовую частоту в ГГц.)

Используемые в микроархитектуре Power9 ядра имеют более специфическую функциональность, чем в других распространенных процессорах — например, в процессорах x86-архитектуры Intel, где процессорные ядра выполняют практически все функции всего процессора. В Power9 SMT-ядра отдают часть функций общему коммутатору.

Предполагается четыре варианта реализации Power9: c SMT4 или SMT8, для одно–двухпросессорных или многопроцессорных систем. С Power9 в первую очередь будут конкурировать серверные процессоры Intel Skylake-SP, также выпускаемые по технологии 14 нм. Ядра Skylake-SP могут работать с более длинными, чем SMT4 и SMT8, векторами и получать 32 DP-результата за такт (https://software.intel.com/en-us/articles/intel-xeon-processor-scalable-family-technical-overview), а в старшей 28-ядерной модели это дает 896 DP-результатов за такт. Поскольку достигаемые тактовые частоты сопоставимы, то по пиковой производительности с плавающей запятой Skylake-SP более предпочтительны.

Поэтому для HPC-систем на платформе Power9 целесообразно ориентироваться на гетерогенные конфигурации, в первую очередь с добавлением графических процессоров Nvidia (для этого в Power9 и интегрирован интерфейс NVLink 2.0). Однако Power9 предназначен и для систем, работающих в гипермасштабируемых облачных ЦОД, где процессор имеет ряд преимуществ: ввод-вывод (работа через PCIe v4 против PCIe v3 в Skylake); организация больших SMP-систем на базе SMT8 с повышенной пропускной способностью и емкостью оперативной памяти; огромный кэш L3 (120 Мбайт против 38,5 Мбайт в Skylake-SP); доступ к FPGA.

***

Процессор Power9 вместе с Nvidia V100 (Volta) будет применяться в вычислительных узлах суперкомпьютеров Summit и Sierra в знаменитых Окриджской и Ливерморской национальных лабораториях США, что уже говорит само за себя. Данных по производительности в тестах систем на Power9 еще нет, однако, например, схожая по архитектуре конфигурация на базе гетерогенных вычислительных узлов с Power8 и с 4 GPU Nvidia P100 на 64 узлах демонстрирует ускорение 95% от линейного (https://www.top500.org/news/ibm-pushes-envelope-in-deep-learning-scalability/).

Литература

- Sadasivam S. K. et al. IBM Power9 Processor Architecture // IEEE Micro. — 2017. Vol. 37, N. 2. — P. 40–51.

- Михаил Кузьминский. Пополнение в семействе Power // Открытые системы.СУБД. — 2014. — №7. — С. 16–18. URL: https://www.osp.ru/os/2014/07/13042909 (дата обращения: 18.09.2017).

- Jeff Stuecheli. Power9 (2016). POWER Systems, IBM Systems.

Михаил Кузьминский (kus@free.net) — сотрудник, Институт органической химии РАН (Москва).