На этой встрече обсуждалась среднесрочная перспектива развития многоядерных процессоров, однако, хотя речь шла о недалеком будущем, не удалось достичь согласия относительно развития событий в ближайшем десятилетии: количество мнений было равно числу участников.

На этой встрече обсуждалась среднесрочная перспектива развития многоядерных процессоров, однако, хотя речь шла о недалеком будущем, не удалось достичь согласия относительно развития событий в ближайшем десятилетии: количество мнений было равно числу участников.

Чак Мур из AMD утверждал, что будущее в гетерогенности – процессоры будут собирать из различных по размеру и функ-циональности ядер, каждое из которых программируется отдельно. Системное единство обеспечивается общим интерфейсом прикладного программирования (API), расположенным на уровень выше машинных команд, и, как следствие, возможен полный пересмотр представлений о совместимости – переход от общей для семейства процессоров системы команд к общему стандарту на интерфейс. Эту точку зрения поддержал специалист из японской компании Renesas Technology, производящей гетерогенные двухъядерные процессоры со встроенной флэш-памятью, предназначенные для работы в составе автомобильного навигационного оборудования.

Бред Маккреди, главный инженер по микропроцессорам корпорации IBM, занял компромиссную точку зрения, согласующуюся с архитектурой 9-ядерного процессора Cell – одно универсальное ядро Power Processor Element (PPE) и восемь специализированных ядер Synergistic Processing Elements (SPE).

Анант Агарвал, профессор из МТИ и основатель компании Tilera, продвигал гомогенный подход, заявив, что в 2017 году процессор для встроенных систем будет состоять из 4096 ядер, серверный процессор – из 512 ядер, а процессор для ПК – из 128 ядер. Агарвал считает, что вопрос не в том, когда случится количественный прорыв, а в том, готовы ли мы к столь радикальным переменам. Главный технолог Sun Рик Хетерингтон, также приверженец гомогенного подхода, был менее амбициозен, ограничивая число ядер в серверных процессорах к 2018 году диапазоном от 32 до 128, но предсказывая более быстрый рост числа потоков – до 1000 на одно ядро. Уверенность в этом основывается на способности уже существующего ПО поддерживать такое количество потоков. Однако остается огромное число приложений, которые не делятся на потоки. На это Маккреди сказал, что нельзя всем равняться на Google, где все написано с нуля, – в большинстве ЦОД останутся старые «тупые» приложения, исходные коды к которым давно утеряны, но которые еще долго будут работать. Точку в этой ветке дискуссии поставил Дэвид Дитцел, основатель Transmeta и автор наделавшего немало шума процессора Crusoe, напомнивший, что с момента появления первого 64-разрядного процессора Sun и до выпуска операционной системы, способной его поддерживать, прошло десять лет.

Итак, что же нас ждет, «гомо» или «гетеро»? С общих позиций понятно, что только многоядерные технологии позволяют справиться с постоянным ростом числа транзисторов. Многоядерность неизбежна, но остается открытым вопрос, какой она будет. Ясно, что на протяжении ближайших полутора десятилетий нас ждут большие перемены, и, как метафорично выразился Патрик Гелсингер из Intel: «Они (перемены) накатывают с неотвратимостью грузового поезда».

По закону Амдала

Складывается впечатление, что никто из участников дискуссии не пытается посмотреть, как можно сравнить между собой разные многоядерные архитектуры, а ведь на самом деле есть интересные работы, и одна из них, «Закон Амдала в многоядерную эру» (Amdahl’s Law in the Multicore Era) Марка Хилла и Майкла Марти, неплохо расставляет точки над i.В 2007 году она была опубликована впервые в виде отдельного отчета, а в июле 2008-го перепечатана в журнале Computer. Видимо, прав известный исследователь из IBM Томас Пузак: «Всем известен закон Амдала, но о нем быстро забывают».

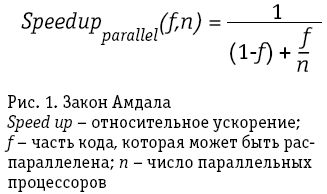

Джин Амдал сформулировал закон в 1967 году, обнаружив простое по существу, но непреодолимое по содержанию ограничение на рост производительности при распараллеливании вычислений:

«В случае, когда задача разделяется на несколько частей, суммарное время ее выполнения на параллельной системе не может быть меньше времени выполнения самого длинного фрагмента». Если разделяемая часть кода f может быть равномерно формально распределена по n процессорам, то закономерность может быть записана, как представлено на рис. 1.

Закон определяет теоретически возможную верхнюю границу, но на практике дело обстоит еще хуже – часть ресурсов каждого процессора уходит на обеспечение коллаборативной работы, а шины обладают конечной пропускной способностью.

Единственная известная гипотеза о возможности преодоления описанных ограничений была высказана в 1988 году Джоном Густафсоном, но она не распространяется на подмножество фиксированных задач. На основании полученного опыта Густафсон пришел к выводу, что при построении более мощных систем пользователи стремятся не сократить время работы текущей версии задачи, а перейти к новой версии, обеспечивающей более высокое качество решения:

S(P)= P – l(P – 1), где P – число процессоров, S – ускорение, l – часть кода, не поддающаяся распараллеливанию.

Допустим, некоторую конструкцию можно рассчитать методом конечных элементов, и в таком случае, чем меньшим берется размер элемента, тем выше будет точность. Сегодня идеи Густафсона, связанные с совершенствованием методов коммуникации между узлами, реализуются в компании Massively Parallel Technologies (MPT), где, кстати, работает и сам Амдал. Допустимо сказать, что эти методы позволяют преодолеть ограничения закона, названного его именем, но только косвенно.

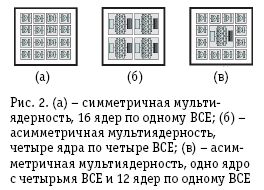

Принцип замены простых задач более сложными, предложенный Густафсоном, скорее экзотика, чем повседневная практика, поэтому в массовых приложениях, на которые рассчитываются многоядерные процессоры, действует закон Амдала. Для анализа многоядерных процессоров Хилл и Марти предложили свою методику декомпозиции процессоров и свою единицу измерения ресурсов, которую они назвали Base Core Equivalent – «основной ядерный элемент». В состав BCE входят все ресурсы, которые являются атрибутами собственно ядер, а общие для ядер системные ресурсы, такие как разделяемый кэш, интерконнект и контроллеры памяти, в него не включаются. В зависимости от технологии чип может содержать n штук BCE, из которых можно собрать различное количество ядер. Группировка BCE в ядра может быть симметричной (гомогенной), асимметричной (гетерогенной) и динамической, изменяемой (рис. 2).

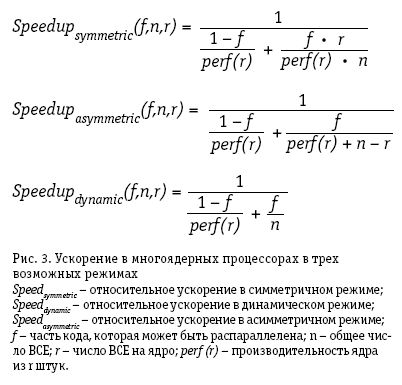

На рис. 3 приведены расчетные формулы ускорения в трех возможных режимах.

Анализ трех зависимостей подтверждает очевидный вывод: хуже всего к нагрузке, имеющей значительную долю крупных фрагментов, приспособлен симметричный режим, лучше – асимметричный и идеально – динамический. Именно динамический режим с возможностью переконфигурирования в соответствии с изменениями нагрузки следует рассматривать в качестве идеальной цели. Разумеется, пока он еще недостижим, поэтому будущее, скорее всего, за ассиметричным или гетерогенным режимом.

Разные типы асимметрии

Примером простого гетерогенного решения может быть чип Cell (Cell Broadband Engine Architecture, Cell BE), спроектированный совместно компаниями Sony, Toshiba и IBM. Простой можно назвать идею объединения ядер двух типов, а о подлинной серьезности проекта можно судить по тому, что начиная с 2001 года над ним работает более 400 инженеров, а затраты на исследования и разработки заметно превышают полмиллиарда долларов. Процессор состоит из одного универсального ядра Power Processor Element (PPE) и множества специализированных ядер Synergistic Processing Elements (SPE). PPE и набор SPE объединены шиной Element Interconnect Bus (EIB). Сейчас ядра SPE способны работать с числами одинарной точности, но скоро появится версия, поддерживающая двойную точность. Первым приложением Cell, как известно, стали игровые приставки, что было необходимо для обеспечения массовости производства, однако замыслы идут гораздо дальше – к петафлопным вычислениям (в 2008 году был запущен суперкомпьютер IBM Roadrunner с пиковой производительностью 1,7 PFLOPS). Счетными задачами область приложения Cell и его преемников не ограничивается: ведущий разработчик SPE Питер Хофзее считает, что будущее процессора находится вне традиционной программной парадигмы «операционная система – приложение», что он будет востребован качественно новыми областями применения, возможно, реального времени, например, такими, как распознавание речи, мимики, жестов и эмоций.

Другой подход к асимметрии разрабатывается в AMD и получил название Accelerated Computing, то есть «вычисления с ускорителями», в данном случае с графическими ускорителями (Graphical Processing Unit, GPU). Однако будет неверно связывать этот подход исключительно с AMD. Так, еще в 1999 году израильский филиал Intel разработал процессор Timna, где классическое ядро совмещалось с GPU и контроллером памяти, но в силу каких-то внутренних причин проект развития не получил. Основные качества Accelerated Computing можно сформулировать так:

-

процессор будет включать в себя и универсальные, и специализированные сопроцессоры;

-

для выполнения той или иной задачи будет выбираться процессор или совокупность процессоров, которые являются оптимальными для данного типа приложения;

-

для задач, предназначенных для параллельных вычислений, разработчик получает в руки инструменты высокого уровня – программное обеспечение освобождается от необходимости знать детали работы того или иного процессора.

Появление подхода Accelerated Computing можно рассматривать как конвергенцию двух существовавших почти независимо направлений: универсальные процессоры для универсальных компьютеров и системы на кристалле (System-on-a-Chip, SOC) для встроенных систем управления. При переходе от технологии 90 нм к 65 нм, 45 нм и далее, а также к многоядерным гетерогенным архитектурам различия между ними становятся минимальными, в SOC для управления могут привлекаться сигнальные процессоры, конвертеры и другие компоненты, неиспользуемые в универсальных компьютерах. Тот факт, что AMD активнее и раньше других вступила на этот путь, можно объяснить последовательно проводимой технической политикой. В 2003 году компания купила у National Semiconductor бизнес, связанный с производством процессоров Geode, совместимых с x86 и предназначенных для встроенных SOC, и нынешний Athlon многое позаимствовал у Geode NX. В 2006 году была куплена ATI Technologies, один из двух крупных производителей графических ускорителей. Ее основной продукт Radeon был единственным, способным составить конкуренцию nVidia. Для объединения процессоров в SOC компания AMD имеет наработки, связанные с магистралью передачи данных HyperTransport. Пока таким комплексом технологий не обладает ни один из производителей микросхем.

Задачу Accelerated Computing можно представить как проектирование гетерогенных многоядерных схем. При необходимости в кристалл могут добавляться специализированные ядра, или же они могут подключаться как внешние ускорители. С программной точки зрения Accelerated Computing поддерживается инструментальными средствами высокого уровня с необходимыми API. Сочетание мощных CPU с GPU позволит решать и задачи с большим количеством последовательных кодов, удовлетворяя требованиям закона Амдала

и обрабатывая с высокой скоростью коды, которые могут быть распараллелены.

Программное обеспечение многоядерных систем

Массовое применение многоядерных систем стало реальностью, однако их триумфальному шествию могут помешать ограничения и нерешенные проблемы программного обеспечения.

Новая эра в оценке производительности компьютерных систем

Традиционные методики оценки производительности компьютерных систем постепенно теряют свою эффективность – компьютеры все активнее взаимодействуют друг с другом, людьми и внешним миром, что приводит к появлению стиля компьютерной обработки, определяемой сценариями развития событий, а это открывает эру новых интеллектуальных устройств и одновременно порождает совершенно новые потребности в оценке их производительности.