Архитектура ccNUMA в исполнении Sun Microsystems

Флагманом многопроцессорных вычислительных систем с общим полем памяти в линейке серверов компании Sun Microsystems стал Sun Fire 15K, известный также под своим кодовым названием Star Cat и пришедший на смену UltraEnterprise 10000 [1].

Флагманом многопроцессорных вычислительных систем с общим полем памяти в линейке серверов компании Sun Microsystems стал Sun Fire 15K, известный также под своим кодовым названием Star Cat и пришедший на смену UltraEnterprise 10000 [1].

Особый интерес к Sun Fire 15К связан с тем, что это последняя по времени появления система ccNUMA-архитектуры, базирующаяся на 64-разрядных микропроцессорах; подобные системы предложили уже почти все ведущие разработчики (SGI Origin 3000 [2], Сompaq GS320 [3], HP Superdome [4]). Еще одна причина подобного интереса — намерение большинства ведущих производителей отказаться в ближайшем будущем от разработок собственных 64-разрядных RISC-процессоров в пользу IA-64; между тем, линия процессоров Sun UltraSPARC будет развиваться.

Сегодня стало уже общепринятым, что в многопроцессорных системах с общим полем памяти для достижения наилучшего масштабирования необходимо отказаться от классической архитектуры SMP (узким местом которой является общая шина или коммутатор) в пользу ccNUMA. В последнем случае многопроцессорные системы строятся на базе SMP-узлов, содержащих процессоры и оперативную память, а узлы связываются между собой посредством общесистемного межсоединения, в роли которого обычно выступает коммутатор. Поэтому доступ процессоров к локальной оперативной памяти своего узла осуществляется быстрее, чем к оперативной памяти другого узла; таким образом, доступ оказывается «неоднородным», о чем и говорит сокращение NUMA (Non-Unifrom Memory Access), а сс означает coherent cash («когерентный кэш»). Замедление доступа к удаленной оперативной памяти — это плата за масштабируемость, и разработчики стремятся по возможности нивелировать различия в скорости доступа к локальной и удаленной памяти.

В [2-5] рассмотрены рассмотрены типичные особенности архитектуры сcNUMA, включая вопросы поддержания когерентности кэша, обеспечение минимизации задержек по обращению в оперативной памяти и т.д. Было показано, что рассматриваемые системы имеют много общих архитектурных черт, базируясь на применении многоуровневой системы коммутаторов. Sun Fire 15К также имеет многие из этих особенностей.

Общая архитектура Sun Fire 15К

Архитектуру серверов Sun Fire 15К определяют две группы особенностей. Одна связана с общими принципами построения систем ccNUMA, а другая — с особенностями применения UltraSPARC III. Последнее во многом определяет основные черты, отличающие Sun Fire 15К от других систем архитектуры ccNUMA.

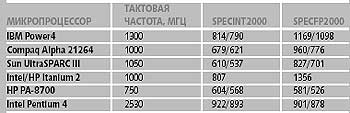

UltraSPARC III — 64-разрядный суперскалярный RISC-процессор, способный выполнять 4 команды за такт. Несмотря на относительно более простую схему организации выполнения команд по сравнению с суперскалярными процессорами, поддерживающими внеочередное выполнение инструкций (HP PA-8x00, Alpha 21264 и др.), UltraSPARC III обеспечивает высокий уровень производительности (табл. 1).

|

| Табл. 1. Производительность некоторых микропроцессоров на тестах SPECcpu2000 (пиковое/базовое значения) |

|

| Рис. 1.Блок-схема процессора UltraSPARC III |

На рис. 1 представлена блок-схема UltraSPARC III [6, 7] части его взаимодействия со связанными с ним компонентами Sun Fire 15К. Кроме кэша второго уровня емкостью 8 Мбайт здесь представлены двухпроцессорный коммутатор (он является аналогом системной шины и подключается к межсоединению Fireplane) и оперативная память.

Встроенный в UltraSPARC III контроллер оперативной памяти управляет двумя группами модулей DIMM SDRAM, объединенных в четыре банка. Пиковая пропускная способность одного банка составляет 0,8 Гбайт/с, а суммарная — 2,4 Гбайт/с. Подобная ситуация типична для многопроцессорных систем с общим полем памяти. Применяемые технологии оперативной памяти отстают от последних достижений (DDR SDRAM, RDRAM) из-за больших сроков разработки, и высокая пропускная способность поддерживается за счет специальных архитектурных решений (например, расслоение, или перекрытие памяти). Интеграция в микропроцессор контроллера оперативной памяти, тегов внешнего кэша и средств управления «когерентностью» при работе с Fireplane служит очевидной цели — уменьшению задержек.

Если обратиться теперь к общей схеме построения Sun Fire 15K, то она основана на многоуровневой системе коммутаторов. На верхнем уровне находится собственно системное межсоединение Fireplane. В слоты Fireplane вставляются так называемые платы расширения (expander), также своего рода коммутаторы. К каждой плате расширения подсоединяется процессорная плата (назовем ее платой P/M), содержащая процессоры и оперативную память, и плата ввода-вывода (I/O). Платы P/M используют разъем типа Slot0, платы I/O — типа Slot1. Коллекцию из трех плат (платы P/M, I/O и плата расширения) в Sun называют «набором плат».

В мощных многопроцессорных серверах шины данных обычно отделены от адресных шин. В серверах Sun это разделение имело место и ранее, в частности, в архитектуре UPA [1, 6], развитием идей которой является Fireplane. При этом организация потоков данных может существенно отличаться от организации потоков адресной информации, поэтому в необходимых случаях для упрощения соответствующего описания будем изображать архитектурные блоки рассматриваемых серверов двояко — с точки изображения потоков данных и с точки зрения организации управления.

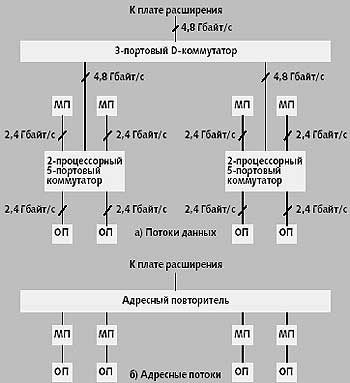

Из рис. 2а ясно, что платы P/M несколько отличаются от аналогичных плат — узлов SGI Origin 3000, ячеек HP Superdome и блоков QBB в серверах Compaq GS [2-4]. Эти отличия связаны со своего рода «неоднородностью» процессоров внутри платы P/M, которые разбиты на пары, соединенные между собой 3-портовым коммутатором данных (далее для краткости будем говорить о D-коммутаторах), а внутри пары используется «двухпроцессорный» 5-портовый коммутатор. Этот коммутатор уровня 0 имеет четыре порта с пропускной способностью 2,4 Гбайт/с (два — для процессоров и два — для памяти) и один порт с пропускной способностью 4,8 Гбайт/с к 3-портовому D-коммутатору уровня 1. Последний коммутатор имеет также порт с пропускной способностью 4,8 Гбайт/с к 3-портовому коммутатору уровня 2 в плате расширения.

Преимуществом плат P/M по сравнению с аналогичными 4-процессорными архитектурными блоками конкурентов является самый высокий уровень пиковой пропускной способности оперативной памяти — 9,6 Гбайт/с. Это значение достигается, в частности, когда все процессоры обращаются к локальной памяти или к памяти своих соседей по паре. Соответственно в полной конфигурации с 18 наборами плат суммарная пиковая пропускная способность памяти достигает 172,8 Гбайт/с. В самом же плохом случае — когда все процессоры обращаются к оперативной памяти в другой половине платы P/M — пропускная способность при обращении к локальной для платы памяти составляет 4,8 Гбайт/с. Когда оперативная память имеет 16-кратное расслоение (это типичный случай), ее пиковая пропускная способность достигает 6,7 Гбайт/с.

Потенциальным недостатком такой архитектуры является некоторое возрастание задержек при обращении процессоров к локальной для платы P/M памяти, но не подсоединенной к тому же двухпроцессорному коммутатору, что и процессоры. Однако возрастание задержки практически незаметно: с 180 до 207 нс.

Что касается емкости оперативной памяти, то при «заселении» всех 8 слотов DIMM, управляемых каждым процессором, модулями емкостью 1 Гбайт, на плату P/M придется 32 Гбайт памяти.

|

| Рис. 2. Архитектура плат P/M |

Взглянем теперь на строение платы P/M с точки зрения работы с адресной информацией (рис. 2б). Для рассылки адресов в платах P/M применяется адресный повторитель, который использует широковещательную рассылку адресной информации внутри платы P/M, а также при работе с платой I/O.

|

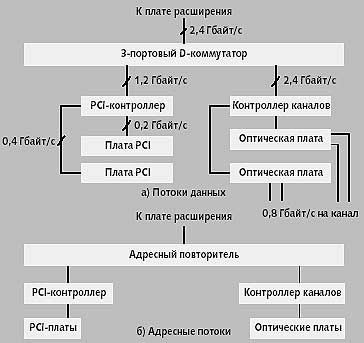

| Рис. 3. Архитектура плат I/O |

Платы I/O имеют собственный порт с пропускной способностью 2,4 Гбайт/с на 3-портовом D-коммутаторе на плате расширения (рис. 3, рис. 4). Плата I/O содержит в типичном случае два симметричных PCI-контроллера (на рис. 3 изображена другая конфигурация, см. ниже), обеспечивающих возможности горячей замены. Каждый контроллер поддерживает одну шину PCI-32 с частотой 33 МГц и одну шину PCI-64 c частотой 33/66 МГц, причем на каждую шину приходится по одному слоту (итого четыре слота на плату I/O).

По сравнению с другими конкурентами ccNUMA-архитектуры число PCI-слотов в узле (наборе плат) Sun Fire 15K невелико. Можно предположить, что, поскольку сервер конструировался позднее, разработчики посчитали, что современные высокопроизводительные шины и протоколы ввода/вывода и высокоскоростные сетевые платы имеют пропускную способность, достаточную для насыщения шины PCI, поэтому больше слотов делать не следует. Однако и число PCI-шин у некоторых конкурентов, например, у HP Superdome, выше. Возможно, сказались и конструктивные ограничения: центральная плата и наборы плат целиком размещаются в одной стойке, расширения не допускаются.

Вместо одного из PCI-контроллеров на плате I/O может располагаться специальный контроллер каналов, к которому подключаются высокоскоростные сетевые платы, работающие с оптоволоконными каналами (рис. 3).

Как части набора плат, плата Р/М и плата I/O подсоединяются к плате расширения (рис. 4), имеющей 3-портовый D-коммутутор с внешним портом к D-коммутатору системного межсоединения Fireplane; пиковая пропускная способность порта равна 4,8 Гбайт/с. Кроме того, плата расширения осуществляет управление потоками адресной информации, обеспечивая широковещательную рассылку этой информации внутри набора между платами P/M и I/O. Поддержание когерентности кэша внутри набора плат осуществляется на базе широковещательного протокола.

Системное межсоединение Fireplane фактически состоит из трех 18-портовых коммутаторов: D-коммуаттора, адресного коммутатора и коммутатора ответов (некоторые функции последнего ниже будут продемонстрированы на примере). D-коммутатор платы расширения подсоединяется к D-коммутатору Fireplane, а блок управления адресной информацией платы расширения — к адресному коммутатору и коммутатору ответов (рис. 4). Каждый порт D-коммутатора Fireplane имеет ширину 32 байта и работает на частоте 150 МГц, что дает пропускную способность порта 4,8 Гбайт/с.

Таким образом, в рассматриваемых серверах мы имеем четыре уровня D-коммутаторов: уровень 0 — 5-портовый D-коммутатор (двухпроцессорный); уровень 1 — 3-портовые D-коммутаторы плат P/M и I/O; уровень 2 — 3-портовый коммутатор платы расширения и уровень 3 — D-коммутатор Fireplane. Половинная пропускная способность последнего равна соответственно 43,2 Гбайт/с. Другие величины пропускной способности, относящиеся к межсоединению, приведены в табл. 2 [8].

|

| Таблица 2. Пиковые значения пропускной способности оперативной памяти (NB — число наборов плат в системе) |

|

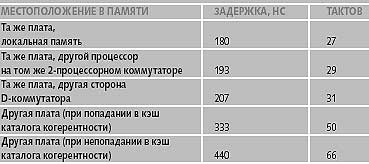

| Табл. 3. Задержки по обращению в оперативную память |

Большое число коммутаторов может вести к сильной дифференциации задержек при обращении к разным местам в оперативной памяти. Однако, как видно из табл. 3, даже при обращении в удаленную память (на другой плате P/M) задержка больше локальной, грубо говоря, вдвое. Это близко к лучшему результату других систем ccNUMA (для HP Superdome [4]). Кроме того, и сама величина локальной задержки ниже, чем у конкурентов (180 нс против 260 нс в HP Superdome). Задержка по обращению в удаленную память в HP Superdome составляет 350-415 нс [4], а в Sun Fire 15K — от 333 до 440 нс. Низкие величины задержек и их не слишком большой рост «по мере удаления» связаны, вероятно, и с небольшим числом портов используемых коммутаторов.

Впрочем, к этим числам следует относиться с осторожностью из-за различных методик оценки, применяемых фирмами-разработчиками. Представленные в табл. 3 данные относятся к «лучшим случаям» доступа одного процессора к оперативной памяти.

Адресные компоненты межсоединения являются трехуровневыми [8]. На нижнем уровне это адресные повторители в наборе плат; на следующем уровне (уровень плат расширения) — адресный контроллер, и на верхнем уровне Fireplane — два коммутатора для адресов и ответов.

Для поддержания когерентности кэша в ccNUMA-системах обычно применяется схема, основанная на специальной кэшируемой памяти каталогов [3, 5].

В SunFire 15K на уровне набора плат (внутри набора плат) применяется широковещательный протокол, а для обеспечения когерентности кэшей между различными платами P/M — каталоги (directories) [6]. Поддержание когерентности кэша является одним из основных «узких мест» архитектуры больших систем ccNUMA. Остановимся на реализации этого механизма в Sun Fire 15K подробнее.

Когерентность кэша

Механизм обеспечения когерентности кэш-памяти, основанный на широковещательной рассылке (snoopy), обеспечивает, как известно, минимальную возможную задержку и пропускную способность, равную

ПС = W x частота_шины/N

где W — ширина строки кэша (64 байт для Ultra SPARC III), а N — число тактов на snoopy-транзакцию. Максимально допустимое число транзакций в секунду на одну адресную шину в Fireplane составляет 150 млн., что примерно втрое выше, чем в предыдущей архитектуре UPA [6]. Оценка пиковой пропускной способности для Fireplane-систем составляет соответственно 9,6 Гбайт/с.

Применяемый механизм обеспечения когерентности основан на известной схеме MOESI и применяется в серверах среднего класса Sun Fire 6800, содержащих до 24 процессоров. В данном механизме snoopy-транзакции обрабатываются всеми устройствами системы, а в более общем случае, каким является Sun Fire 15K, — всеми устройствами домена когерентности. Результаты обработки snoop-транзакции появляются на выходе устройств через 5 тактов после получения ими адреса; общий результат транзакции формируется выделенной микросхемой каждой платы и отправляется обратно в устройства через 4 такта.

Адресная шина реализована в виде двухуровневой древовидной структуры адресных повторителей с распределенной схемой арбитража [6].

Протокол на основе каталогов (специальная память, показывающая, какие устройства системы разделяют или являются собственниками строки кэша) отличается уменьшенным трафиком обеспечения когерентности, так как адреса передаются только тем устройствам, про которые известно, что им эта строка кэша «интересна». Однако подобный механизм дает более высокие задержки, чем механизм snoopy [6]. Поэтому сочетание в Sun Fire 15K широковещательного протокола в наборе плат и протокола на основе каталогов (протоколом типа «точка-точка», P2P) — на более высоком уровне коммуникаций представляется необходимым компромиссом, поскольку иначе нужного уровня пропускной способности в больших системах не достичь.

За поддержание P2P-когерентности между наборами плат (в данном контексте — доменами со snoopy-когерентностью) отвечают блоки, именуемые агентами SSM (Scalable Shared Memory), а реализованная версия Р2Р-протокола получила название SSM-протокола.

SSM-протокол использует хранимые в памяти теги (М-теги) для указания глобального состояния каждого блока памяти емкостью 64 байт. Эта информация находится в оперативной памяти, так как она имеет большой объем. Каждый SSM-агент имеет собственный кэш каталога когерентности для обеспечения более быстрого доступа к «самой свежей» информации о когерентности. М-теги являются дополнительными (по отношению к MOESI-состоянию) описателями состояния строк памяти. Рассмотрим теперь два примера обработки транзакций Fireplane.

I. Передача внутри домена когерентности (аналог обычной SMP-cистемы). При этом запрашиваемый адрес широковещательным образом рассылается по локальной адресной шине, и системные устройства «обнюхивают» (snoop) свою собственную кэш-память на предмет соответствия запросу. Затем 64-байтный блок возвращается из памяти запросившему процессору через коммутатор данных.

- Такты 0-2. Запрос адреса производится запрашивающим процессором и посылается адресному повторителю платы, а тот перенаправляет запрос адресному повторителю верхнего уровня.

- Такты 3-6: широковещательная рассылка адреса адресным повторителем верхнего уровня. Он посылает запросы обратно - адресным повторителям уровня плат. Каждое системное устройство получает адрес на 6-м такте.

- Такты 7-15. Каждое системное устройство проверяет теги когерентности для определения состояния строки кэша в соответствии с протоколом MOESI. На 11-м такте все устройства шлют свой snoop-результат своему D-коммутатору платы. Они обмениваются результатами, рассчитывают глобальный snoop-результат и посылают его устройствам системы на 15-м такте. Если этот результат отвечает попаданию в кэш, с 16-го такта начинается передача из кэша в кэш, и такты обращения к оперативной памяти отсутствуют [6].

- Такты 7-22: чтение из памяти. Целевой контроллер оперативной памяти в соответствующем процессоре распознает, что запрос попал в его диапазон адресов, и запускает чтение из памяти. На такте 22 блок данных посылается из модулей DIMM в локальный двухпроцессорный D-коммутатор.

- Такты 23-36: передача данных. Блок данных передается через ряд D-коммутаторов. На тактах 33-36 четыре 18-байтные порции блоков данных достигают процессора.

Таким образом, 15 тактов системы (100 нс) требуется адресному межсоединению, чтобы получить глобальный (для данного домена) snoop-результат и отправить его системным устройствам. Доступ к памяти запускается частично во время snoop-процесса и требует 7 тактов (47 нс) после завершения snoop-процесса. Передача данных требует разное число тактов в зависимости от того, через сколько D-коммутаторов при этом придется пройти [6].

II. Передача данных между доменами когерентности. В этом случае SSM-агент на локальной адресной шине запрашивающего процессора перенаправит запрос нужному SSM-агенту другого домена. Процедура будет выглядеть примерно так, как описано ниже [6].

- Запрос адреса (такты 0-2). Процессор определяет, что требуемое местоположение оперативной памяти находится вне локального домена когерентности (информация о диапазоне физических адресов домена когерентности хранится в специальных регистрах процессора). Процессор делает запрос к адресному повторителю платы, а тот перенаправляет запрос к адресному повторителю высшего уровня.

- Посылка адреса другому SSM-агенту (такты 3-8). Адресный повторитель делает широковещательную транзакцию, на которую отвечает только SSM-агент. По физическому адресу он определяет целевую плату, и шлет запрос ее SSM-агенту через адресный коммутатор.

- На тактах 9-11 SSM-агент целевой платы "повесит замок" на строку, так, что ни одна другая транзакция к этой строке памяти не будет выполняться. SSM-агент проверяет свою кэш-память каталога когерентности. Если фиксируется непопадание в этот кэш, то SSM-агент будет ждать 16 тактов системы (107 нс), пока М-теги не поступят из памяти.

- SSM-агент целевой платы направляет специальные ответы через коммутатор ответов запрашивающему SSM-агенту.

- На тактах 12-14 SSM-агент целевой платы делает широковещательную рассылку на своей адресной шине.

- На тактах 15-23 все системные устройства домена проверяют свои теги когерентности, чтобы найти, кто является собственником кэша, и этот собственник выдает данные.

- Если данных в кэшах не нашлось, на тактах 15-30 идет запрос в оперативную память, и соответствующий контроллер памяти читает оттуда данные и шлет их в локальный двухпроцессорный D-коммутатор.

- На тактах 31-34 данные направляются к так называемому локальному агенту данных, а на тактах 35-41 они пересылаются через D-коммутатор центральной платы.

- На тактах 42-50 агент данных запрашивающего домена когерентности буферизует данные, извещает о прибытии запрашивающий SSM-агент и отправляет данные по назначению, когда будет доступен соответствующий путь.

- Запрашивающий SSM-агент подсчитывает ожидаемые ответы от целевого SSM-агента (см. выше). Затем запрашивающий SSM-агент извещает целевой SSM-агент через коммутатор ответов, что можно снять замок со строки, и целевой агент выполняет это. Целевой агент при необходимости изменяет М-теги.

Заключение

Необходимо сделать еще одно дополнительное замечание, касающееся архитектуры и конфигурации серверов. Кроме плат I/O, имеются еще платы MaxCPU — с тем же типом разъема Slot1, что и платы I/O. Платы MaxCPU содержат по два процессора и могут использоваться в наборах плат вместо плат I/O. В результате общее число процессоров в системе может достигать 106. Максимальная емкость оперативной памяти Sun Fire 15K — 576 Гбайт, емкость дискового пространства — до 250 Тбайт.

Литература

- Михаил Кузьминский, Серверы UltraEntreprise 10000. // Открытые системы, № 5, 1997, стр. 13-17

- Михаил Кузьминский, Серверы нового поколения архитектуры NUMA компании SGI. // Открытые системы, 2000, № 9, стр. 10-15

- Михаил Кузьминский, Особенности архитектуры серверов Compaq GS. // Открытые системы, 2001, № 1

- Михаил Кузьминский, Архитектура серверов HP Superdome. // Открытые системы, 2000, № 11, стр. 9-13

- Михаил Кузьминский, "Архитектура S2MP - свежий взгдяд на ccNUMA". Открытые системы, 1997, № 2, стр. 14-21

- A. Charlesworth, "The Sun Fireplane System Interconnect". Supercomputing'2001, Nov. 2001

- Михаил Кузьминский, Микроархитектура UltraSPARC III. // Открытые системы, 1998, № 4, стр. 22

- Sun Fireplane 15K System, Overview. Sun Microsystems, Nov. 2001