Именно эти тенденции привели в конце 1999 года к образованию компании Fujitsu Siemens Computers. В результате появилась новая транснациональная компания, владеющая значительной долей мирового рынка серверов и сильными позициями в Европе. Хотя вновь образованная компания предлагает широкий спектр изделий и услуг в сфере информационных технологий, в данной статье рассматриваются только архитектурные особенности предлагаемых ею новых Unix-систем серии GP7000F и их основные отличия от соответствующих изделий компании Sun Microsystems

Основа систем GP - новый 64-разрядный процессор SPARC64-GP, разработанный компанией HAL Computers из группы компаний Fujitsu, и ОС Solaris, дополненная технологиями построения систем высокой готовности и высокопроизводительных кластеров от Fujitsu и Siemens.

Выбор архитектуры SPARC для компании Fujitsu вовсе не случаен. Именно Fujitsu изготовила первый процессор SPARC на базе вентильной матрицы, работающей на частоте 16,67 МГц. На основе этого же процессора была создана первая рабочая станция Sun-4 с производительностью 10 MIPS, объявленная осенью 1987 года. В марте 1988 года Fujitsu увеличила тактовую частоту до 25 МГц, создав процессор с производительностью 15 MIPS. Позднее, после разработки компанией Texas Instruments 50-мегагерцевого процессора MicroSPARC, который широко использовался в дешевых моделях рабочих станций SPARCclassic и LX, Sun вместе с Fujitsu создали новую версию этого процессора - MicroSPARC II. На его основе были построены рабочие станции и серверы SPARCstation/SPARCserver 4 и 5, работающие на тактовых частотах 70, 85 и 110 МГц.

В 1995-96 годах компания HAL разработала многокристальные процессоры SPARC64 I и SPARC64 II, реализующие 64-разрядную архитектуру SPARC64 V9. Появившийся в 1998 году новый процессор компании HAL, SPARC64-GP, представляет собой высокопроизводительный суперскалярный процессор, который реализует 64-битовую архитектуру по спецификациям SPARC V9. Процессорный чип SPARC64-GP соответствует техническим требованиям SPARC64 «Level 2» и взаимодействует с шиной UPA (UltraSPARC Port Architecture) и микросхемами SRAM кэш-памяти второго уровня. Микропроцессор SPARC64-GP обеспечивает полную совместимость с аппаратурой и программным обеспечением компании Sun. Кроме того, впервые для HAL кристалл SPARC64-GP обеспечивает возможность построения многопроцессорных систем, что стало обязательным для современных серверов, работающих в корпоративной вычислительной среде.

Особенности архитектуры процессора SPARC64-GP

Наиболее важным архитектурным требованием SPARC64-V9 является двоичная совместимость непривилегированных программ при любых реализациях. Двоичные коды, выполняемые в непривилегированном режиме, должны демонстрировать одинаковое поведение на всех системах SPARC64-V9, работающих под управлением операционной системы, которая предоставляет стандартную среду выполнения программ. Пример такой стандартной среды - двоичный интерфейс приложений ABI (Application Binary Interface), разработанный совместно Sun и Fujitsu.

Процессор SPARC64-GP обеспечивает высокие скорости выполнения команд благодаря реализации следующих основных особенностей:

- Линейное 64-разрядное адресное пространство.

- 32-разрядные команды, выровненные по 32-разрядным границам в памяти. Только команды чтения и записи обращаются к памяти и выполняют ввод/вывод.

- Небольшое число режимов адресации. Формирование адреса памяти осуществляется либо с помощью операции «регистр + регистр», либо с помощью операции «регистр + непосредственная константа».

- Трехадресная система команд. Большинство арифметико-логических команд работает с двумя операндами из регистров или с одним операндом из регистра и непосредственной константой и помещают результат в третий регистр.

- Большой регистровый файл, имеющий оконную организацию. В любой момент времени программа видит восемь глобальных регистров и 24-регистровое окно в большом регистровом файле. Регистры окна можно использовать для кэширования параметров процедур, локальных переменных и адресов возврата.

- Плавающая точка. Архитектура процессора соответствует требованиям стандарта IEEE 754 и обеспечивает реализацию набора команд плавающей точки для работы с отдельным регистровым файлом, который предоставляет 32 регистра одинарной точности (по 32 разряда), 32 регистра двойной точности (по 64 разряда), 16 регистров четверной точности (по 128 разрядов) или смесь этих регистров.

- Быстрая обработка прерываний. Применяется табличный метод обработки прерываний.

- Команды синхронизации процессора. Одна из команд выполняет атомарную операцию с памятью «чтение - установка», другая атомарная операция реализует обмен значений регистра и памяти. Третья операция сравнивает содержимое регистра со значением в ячейке памяти и осуществляет обмен этого значения в памяти с содержимым другого регистра, если сравнение дало совпадение («сравнение и обмен»). Еще два регистра синхронизируют порядок наблюдаемых процессорами операций с общей (разделяемой) памятью.

- Предсказание ветвлений. Команды ветвления с предсказанием направления условного перехода позволяют компилятору или программисту на языке ассемблера дать аппаратуре совет о том будет ли в действительности переход выполняемым.

- Команды ликвидации переходов. Несколько команд могут использоваться для того, чтобы вообще ликвидировать условные переходы, например, команды пересылки по условию. Устранение условных переходов увеличивает производительность суперскалярных и суперконвейерных реализаций.

- Аппаратный стек прерываний. Аппаратный стек прерываний обеспечивает выполнение вложенных прерываний. Он содержит всю информацию о состоянии машины, необходимую для возврата на предыдущий уровень прерывания.

- Менее строгая (ослабленная) модель порядка обращений к памяти - RMO (Relaxed memory order). Эта модель позволяет аппаратуре планировать обращения к памяти почти в произвольном порядке до тех пор, пока программа вычисляет правильный результат.

|

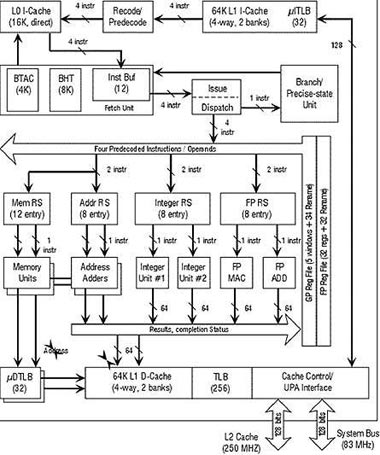

| Рис. 1. Архитектура процессора SPARC64-GP |

Как видно из рис. 1, микропроцессор SPARC64-GP V9 содержит семь основных устройств.

Устройство переходов (BRU). Осуществляет выборку команд, управляет работой счетчика команд (PC) и передает до четырех команд в такт в устройство выдачи команд. Кэш L0 представляет собой кэш-память команд нулевого уровня с прямым отображением, которая имеет емкость 16 Кбайт и обеспечивает выдачу до четырех команд в такт. При возникновении промаха в кэше L0 BRU посылает четыре запроса в кэш первого уровня (L1) для выборки строки, длина которой составляет 64 байта.

Устройство выдачи команд (ISU). Выдает и направляет к месту назначения до четырех команд в такт, а также отслеживает состояние всех активных команд.

Устройство формирования потока данных (DFU). Выполняет команды, используя аппаратные регистры фиксированной и плавающей точки, средства переименования регистров, исполнительные устройства фиксированной и плавающей точки и устройство чтения/записи данных в память.

Кэш команд первого уровня (L1-Cache). Получает от BRU один запрос выборки команд в каждом такте (выдает по 16 байт на каждый запрос), обращается к кэш-памяти команд первого уровня (4-канальная множественно ассоциативная память емкостью 64 Кбайт) и возвращает 4 команды в такт. Когда происходит промах, кэш первого уровня посылает запрос в устройство UC, чтобы получить строку данных длиною 64 байта.

Кэш данных первого уровня (D1-Cache). В каждом такте получает от DFU до двух запросов чтения или записи (каждый запрос представляет собой обращение к данным длиною до 8 байт), обращается к кэш-памяти данных первого уровня (4-канальная множественно ассоциативная память емкостью 64 Кбайт) и считывает один или два элемента данных в каждом такте.

Устройство транзакций (TR). Содержит основное устройство преобразования адресов (Main TLB), включающее 256 элементов. Обращение к TR происходит по запросам на преобразование адресов, поступающих из кэш-памяти L1 или D1. Устройство транзакций возвращает в L1-кэш или в D1-кэш соответствующий элемент таблицы страниц.

Устройство управления кэш-памятью второго уровня и интерфейсом UPA (UC). Управляет внешним общим кэшем второго уровня и интерфейсом шины UPA (кэш второго уровня имеет емкость от 1 до 16 Мбайт и представляет собой кэш-память с прямым отображением). Получает запросы на обработку промаха из кэшей L1 или D1 и возвращает строку кэша (64 байта) в L1 или в D1. При возникновении промаха, чтобы получить соответствующую строку кэш-памяти, UC посылает запрос на шину UPA.

Функциональные устройства

При сравнимых частотах синхронизации процессор SPARC64-GP компании HAL обеспечивает более высокую общую производительность, чем UltraSPARC II от Sun Microsystems. Процессор SPARC64-GP имеет ядро, обеспечивающее внеочередное выполнение команд, способное одновременно обрабатывать до 63 команд, в отличие от процессора UltraSPARC-II, который использует ядро с упорядоченным выполнением команд. Процессор SPARC64-GP имеет также два устройства обработки вещественных чисел и два устройства чтения/записи и обеспечивает, по сравнению с UltraSPARC II, формирование в каждом такте в 1,5 раза большего числа результатов операций с плавающей точкой. Кроме того, кэши команд и данных SPARC64-GP имеют в четыре раза большую емкость и реализованы в виде 4-канальной множественно ассоциативной памяти, что обеспечивает меньшие коэффициенты промахов по сравнению с UltraSPARC II. Более того, SPARC64-GP использует раздельные шины интерфейса с кэшем второго уровня и с системной шиной, обеспечивая более высокую пропускную способность памяти в установившемся режиме по сравнению с UltraSPARC II при сопоставимой частоте синхронизации.

Функциональное устройство плавающей точки (FPU). Выполняет операции над вещественными числами, используя одно устройство умножения-сложения с плавающей точкой (FMA), одно устройство деления с плавающей точкой (FDIV/SQRT) и одно устройство сложения с плавающей точкой (FA).

Устройство FA выполняет команды сложения и вычитания с плавающей точкой и занимает только половину площади устройства умножения-сложения (FMA). Реализация устройства умножения-сложения имеет преимущество по сравнению с простым устройством умножения, поскольку такое устройство может выполнять в каждом такте вторую операцию сложения или вычитания.

Устройство FPU может инициировать в каждом такте одну операцию сложения с плавающей точкой и либо одну операцию умножения-сложения, либо одну операцию деления с плавающей точкой, и может формировать в каждом такте один результат сложения и один результат сложения-умножения или один результат деления с плавающей точкой. Однако когда операции инициированы, устройства FMA и FDIV/FSQRT работают параллельно.

Устройство FMA представляет собой четырехступенчатый конвейер. FMA выполняет также операции пересылки с плавающей точкой длительностью 1 такт. Устройство FA также представляет собой конвейер, но с задержкой в три такта.

Устройство FDIV/FSQRT имеет задержку 12 тактов для операций с одинарной точностью и 22-23 такта для операций с двойной точностью. Устройство FDIV/FSQRT блокирует FMA на один такт для того, чтобы начать операцию деления, и еще на один такт, когда оно помещает результат на шину результата. Во время выполнения операции деления оба устройства FMA и FDIV/FSRT работают параллельно.

Процессор SPARC64-GP имеет ядро, возможности которого превосходят UltraSPARC II, особенно при работе с приложениями, предполагающими интенсивное использование вещественных чисел. Процессор UltraSPARC II имеет отдельные устройства умножения и сложения и позволяет операциям сложения и умножения начинаться в каждом такте. Однако он имеет только одно устройство чтения/записи, лишая устройства плавающей точки адекватной полосы пропускания памяти. Второе устройство плавающей точки в SPARC64-GP вдвое увеличивает количество операций с плавающей точкой, которые могут начинаться в каждом такте.

Функциональное устройство целочисленных операций с фиксированной точкой. Это устройство выполняет целочисленные команды, используя два независимых устройства, реализующие арифметические, логические операции и операции сдвига (ALS). При этом одно из устройств ALS разделяет свои шины операндов и результата с устройством целочисленного умножения/деления (MULDIV). Это комбинированное устройство может в каждом такте инициировать либо одну операцию умножения, либо одну операцию ALS и может формировать один результат MULDIV или ALS в каждом такте. После инициации соответствующей операции, устройство ALS и устройство умножения/деления работают параллельно. Выполнение всех операций ALS осуществляется за 1 такт, поэтому эти устройства не конвейерные.

Операция целочисленного умножения выполняется от 4 тактов (для 32-разрядных операндов) до 6 тактов (для 64-разрядных операндов). Целочисленное деление выполняется от 2 до 37 тактов в зависимости от значения аргументов и составляет в среднем 13 тактов. Устройство умножения/деления «крадет» один такт ALS для помещения результата на шину результата.

Функциональное устройство операций с фиксированной точкой/формирования адреса (FX/AGEN) выполняет целочисленные команды и вычисляет адреса операций чтения/записи, используя два независимых арифметико-логических устройства. В отличие от FXU, FX/AGEN не включает устройств сдвига и умножения/деления. Устройство FX/AGEN используется для вычисления эффективных адресов для операций чтения и записи в память, а также для операций целочисленной арифметики, которым не требуется сдвига, умножения или деления. FX/AGEN может выполнять до двух вычислений в каждом такте.

Функциональное устройство чтения/записи (LSU) выполняет операции чтения и записи, позволяя адресовать четные и нечетные банки кэш-памяти данных первого уровня. LSU отвечает за корректное выполнение операций чтения и записи.

Помимо расширенных возможностей по обработке чисел с плавающей точкой, SPARC64-GP имеет достаточно изощренное ядро для неупорядоченного выполнения команд, позволяющее ему лучше справляться с промахами кэш-памяти по сравнению с UltraSPARC II. Каждое устройство формирования адреса и станции резервирования устройств плавающей точки имеют по 8 элементов и осуществляют диспетчеризацию до двух команд в каждом такте. Поскольку используется переименование регистров, в случае готовности к выполнению более двух команд вообще отсутствуют какие-либо ограничения по неупорядоченной диспетчеризации этих команд, если в соответствующие обрабатывающие устройства направляются две наиболее старые команды. Однако определенные команды чтения/записи должны выполняться в порядке, заданном программой, например, когда модель программирования требует упорядоченного выполнения, или когда команды обращаются к одному и тому же адресу.

Кэш данных первого уровня имеет два банка, расслоенных по 8-байтовым границам для того, чтобы поддерживать два обращения в каждом такте. LSU может выполнять одновременно два обращения по чтению или записи в кэши данных первого уровня в каждом такте, одно к четному кэшу, другое к нечетному. Устройство может также принимать до двух новых запросов чтения или записи в каждом такте. Кэши первого уровня имеют задержку три такта, но они построены по конвейерному принципу, так что в течение каждого такта может начинаться выполнение двух новых обращений и завершаться выполнение двух старых обращений.

Прогнозирование направления переходов

Реализация условных переходов всегда оказывается достаточно накладной для любого суперскалярного процессора и связана с решением ряда проблем:

- Логика прогнозирования переходов центрального процессора может неправильно предсказать направление перехода и начать спекулятивно (по предположению) выдавать команды из неверного пути. Когда определяется правильное направление перехода, спекулятивные команды должны быть сброшены и машина должна восстановиться до состояния, которое существовало на момент выполнения команды перехода. Это приводит к появлению задержки в один или несколько тактов.

- Спекулятивные команды, которые позже аннулируются, могут иметь и побочные эффекты. Например, вызывающая кэш-промах спекулятивная команда чтения создает бесполезную работу для системы памяти. Таким образом, будущим командам обращения к памяти, которые должны будут выполняться безусловно, в случае кэш-промаха придется ждать до тех пор, пока не освободится память. Спекулятивные промахи могут также засорять кэш-память путем замены хороших данных и команд на данные и команды, которые не будут использоваться. Однако во многих случаях предварительно выбранные спекулятивные данные и команды оказываются полезными для будущей работы процессора.

Процессор UltraSPARC II реализует традиционную схему одноуровнего прогнозирования с помощью интегрированной с кэшем команд таблицы истории переходов с двухбитовыми счетчиками. Кэш команд первого уровня в UltraSPARC II имеет емкость 16 Кбайт и построен по схеме двухканальной множественно ассоциативной памяти с физической индексацией и физическим тегированием. При этом длина командной строки кэш-памяти равна 32 байтам и, кроме того, в каждой строке содержится 4 счетчика истории переходов и два поля выборки следующего адреса.

Для увеличения производительности микропроцессор SPARC64-GP использует таблицу истории переходов большего размера и двухуровневую схему прогноза с хешированием адреса перехода 5-битовым «регистром глобальной истории». При этом таблицы истории переходов реализованы отдельно от кэш-памяти команд.

Другим улучшающим работу свойством SPARC64-GP является реализация буфера целевых переходов. В UltraSPARC II таблица целевых адресов переходов также интегрирована с кэшем команд, в то время как SPARC64-GP поддерживает отдельную таблицу.

Организация кэш-памяти

Существенное отличие организации кэш-памяти в процессорах UltraSPARC II и SPARC64-GP заключается в способах аппаратной поддержки адресных синонимов, особенно в кэше данных. В UltraSPARC II кэш данных построен по принципу прямого отображения, индексируется виртуальным адресом и тегируется физическим адресом (VIPT), что создает определенные проблемы с совмещением имен или синонимов. UltraSPARC II не поддерживает механизма «перетегирования» этих синонимов. Чтобы преодолеть этот недостаток, UltraSPARC II расходует два кэшируемых управляющих бита в каждом элементе таблицы преобразования адресов: один для разрешения физического кэша, второй для разрешения виртуального кэша. SPARC64-GP работает более эффективно - за счет аппаратной поддержки перетегирования синонимов без использования дополнительных управляющих битов в элементах таблицы преобразования адресов.

Процессор SPARC64-GP по сравнению с UltraSPARC II не только обеспечивает более высокую полосу пропускания памяти в установившемся режиме, но и более эффективно использует доступную полосу пропускания. Из-за организации сквозной записи в кэше данных, UltraSPARC II может расходовать значительную часть полосы пропускания памяти на выполнение отдельных операций записи в кэш второго уровня. Напротив, кэш данных SPARC64-GP использует стратегию отложенной обратной записи, устраняя тем самым большую часть трафика операций записи в кэш второго уровня. Хотя UltraSPARC II может объединять две записи в одну, а операции записи могут идти последовательно и относиться к последовательным адресам памяти, эффективность такой схемы ограничивается только специальными случаями.

В отличие от UltraSPARC II, который разделяет 128-разрядную шину данных между интерфейсом кэша второго уровня и системным интерфейсом, SPARC64-GP имеет отдельные 128-битовые шины данных для каждого из этих двух интерфейсов. Интерфейс кэш-памяти может работать на полной или на половине скорости процессора, обеспечивая пиковую пропускную способность 4 Гбайт/с при использовании микросхем памяти SRAM, работающих на частоте 250 МГц. Системная шина может работать на скоростях 1/2, 1/3, 1/4 или 1/5 от скорости процессора. Реализация двух раздельных шин устраняет необходимость установки микросхем внешнего буфера данных UDB (UltraSPARC Data Buffer), который требуется для работы UltraSPARC II.

Новое устройство управления памятью (MMU) совместимо с операционной памятью Solaris, но его конструкция проще и базируется на реализации нескольких устройств ассоциативной памяти (TLB) для преобразования виртуальных адресов в физические, а птакже на программном управлении самими TLB. Кроме размеров страниц 8 Кбайт, 64 Kбайт, 512 Kбайт и 4 Mбайт, которые поддерживаются процессором UltraSPARC II, новое устройство MMU поддерживает еще 11 размеров страниц в диапазоне от 4 Kбайт до 4 Гбайт. Размеры страниц более 4 Mбайт были добавлены, чтобы лучше поддерживать крупномасштабные приложения, например, программы операционных систем и баз данных.

Процессор SPARC64-GP имеет три микро-TLB, что позволяет в каждом такте выполнять преобразования трех адресов - одно для обеспечения выборки команд и два для реализации обращений к памяти по чтению/записи. Каждая микро-TLB содержит по 32 элемента, при этом для поддержки 15 различных размеров страниц каждый элемент является полностью ассоциативным. Обращение к памяти, получившее промах в микро-TLB, использует четыре дополнительных такта для поиска соответствующего элемента в основной TLB, которая имеет 256 полностью ассоциативных элементов.

Регистры

В суперскалярном процессоре SPARC64-GP из кэша нулевого уровня в каждом такте выбираются до четырех команд, которые помещаются в 12-элементный буфер. Кэш команд нулевого уровня емкостью 16 Kбайт построен по схеме прямого отображения и содержит перекодированные команды и заранее декодированные биты. На стадиях выдачи и диспетчеризации команд декодируются четыре команды из буфера команд и их регистры результата отображаются на регистры переименования. Кроме того, определяются регистры переименования, которые будут использоваться в качестве источников операндов. Операнды-источники читаются из регистрового файла или из регистров переименования, или пересылаются через шины результата исполнительных устройств. Команды и их операнды в конце стадии диспетчеризации пересылаются на соответствующие станции резервирования (RS).

Каждая RS может принимать по две команды в каждом такте при условии наличия свободного места. Команды чтения/записи пересылаются как на станции резервирования устройства формирования адреса, так и на станции резервирования устройства чтения/записи.

Процессор UltraSPARC II выполняет команды в предписанном программой порядке и не использует регистров переименования. Если какие-либо операнды команды не готовы, UltraSPARC II приостанавливает выполнение этой и всех последующих команд. Он продолжает диспетчеризацию только, когда приостановленная команда готова к выполнению.

Для сокращения простоев конвейера UltraSPARC II должен полагаться на компилятор, который обязан планировать выполнение команд, имеющих большое время выполнения, и команд предварительной выборки данных намного раньше, чем потребуются их результаты. Используя более эффективное ядро, более мощную схему прогнозирования направления переходов, расположенные на кристалле процессора кэши большей емкости, более длинные строки кэш-памяти и аппаратные схемы предварительной выборки, SPARC64-GP работает лучше, чем UltraSPARC II, на серверных приложениях, которые используют большие наборы данных и интенсивные операции с плавающей точкой.

Технология SPARC64-GP

В разработке компании HAL по сравнению с предыдущей многокристальной реализацией на одной подложке интегрированы процессоры второго поколения, два кристалла кэш-памяти с некоторыми усовершенствованиями и новая подсистема управления памятью. Интеграция двух из четырех кристаллов памяти, содержащих по 4,6 млн. транзисторов сокращает емкость каждого кэша первого уровня до 64 Kбайт, но позволяет разместить всю машину на одной подложке площадью 260 кв. мм. Интеграция двух оставшихся кристаллов кэш-памяти дала бы прирост производительности на тестах SPEC95 только на 1-2%, но потребовала бы увеличения площади подложки до 310 мм2.

Использовавшийся ранее кристалл MMU, содержащий два млн. транзисторов, заменен схемами TLB, интерфейса кэша второго уровня и системной шины, которая совместима с шиной UPA компании Sun Microsystems.

Исходный вариант кристалла MMU использовал патентованные интерфейсы для связи с основной памятью и устройствами ввода/вывода, требуя от HAL разработки собственного чипсета. В отличие от этого SPARC64-GP использует системный интерфейс, совместимый с UPA, что позволяет ему спокойно работать с существующими наборами микросхем компании Sun Microsystems. Новый интерфейс существенно упрощает разработку систем на базе кристалла SPARC64-GP.

SPARC64-GP реализован с помощью 0,24-микронного технологического процесса с пятью слоями металлизации CS-70 компании Fujitsu. По сравнению с 1,5 млн. логических транзисторов, используемых для построения схем в процессоре UltraSPARC II, на кристалле размещаются 17,6 млн. транзисторов, из которых 11,6 млн. реализуют кэши и TLB. SPAR64-GP использует 6 млн. транзисторов для реализации своей машины с неупорядоченным выполнением команд. Кристалл монтируется в 957-контактный корпус LGA, используя крепление методом перевернутого кристалла. Максимальная потребляемая мощность составляет 50 Вт при использовании питающих напряжений 3,3 В для ввода/вывода и 2,5 В для ядра. Процессор монтируется на печатную плату с помощью специального переходника, что обеспечивает очень легкую установку и удаление.

На частоте 272 МГц SPARC64-GP показывает производительность 17,6 SPECint95 и 26 SPECfp95 при использовании кэш-памяти второго уровня емкостью 4Мбайт и 60 нс EDO RAM. Разработчики компании HAL ожидают увеличения производительности для систем высшего класса, построенных на базе кристаллов 250 МГц SRAM и обеспечивающих восьмикратное расслоение основной памяти. Эти цифры позволяют оценить уровень производительность 272-мегагерцевого процессора SPARC64-GP, которая оказывается примерно на 30% выше по сравнению с системами, построенными на базе 300-мегагерцевых процессоров UltraSPARC II. Компания HAL продолжает работу над кристаллами SPARC64-GP с 18-микронными проектными нормами, надеясь достичь частоты синхронизации 500 МГц во второй половине текущего года.

Надежность, готовность и удобство обслуживания

Устранение индивидуальных операций записи во внешний кэш упрощает реализацию схем контроля и исправления ошибок (ECC) в кэше второго уровня и на системном интерфейсе, увеличивая надежность систем, построенных на базе SPARC64-GP. Поскольку реализация ECC требует нескольких бит для кодирования группы байт (например, восьми бит для кодирования восьми байт), индивидуальные операции записи, которые осуществляют модификацию меньшего, чем в группе числа байт, требуют реализации операций типа «чтение-модификация-запись» для формирования кодов, корректирующих ошибки.

Поскольку SPARC64-GP одновременно обновляет содержимое целой строки кэш-памяти, он может формировать 16-разрядный код ECC для пересылки каждых 16 байт без использования операций типа «чтение-модификация-запись». Чтобы избежать на интерфейсе этих сложных операций, системы на базе процессора UltraSPARC II в интерфейсе кэша второго уровня используют четность, что приводит к некоторому снижению надежности системы.

В процессоре SPARC64-GP все массивы расположены на кристалле кэшей и TLB также защищаются четностью или ECC. При этом массивы данных защищаются с помощью ECC, а массивы тегов защищаются с помощью четности. В отличие от этого, размещенные на процессорном кристалле массивы в UltraSPARC II, не используют схемы защиты ни по четности, ни по ECC. Более того, именно кэш второго уровня, защищенный простой четностью, делает UltraSPARC II менее приемлемым для критически важных приложений.

Производительность

Первые системы SPARC64-GP имели частоту синхронизации 248 МГц и были разработаны для конкуренции с процессорами UltraSPARC II, работающими на тактовой частоте 300-360 МГц. Таблица 1 дает возможность сопоставить основные параметры этих процессоров, в частности, структура шины кэша и системной шины позволяет SPARC64-GP достичь пропускной способности 4,3 Гбайт/с по сравнению с 2,88 Гбайт/с в UltraSPARC II. Следует, однако, отметить, что оценочные тесты SPEC95 могут быть неадекватной мерой для кристаллов, разработанных для обработки большого числа операций с плавающей точкой и операций с базами данных. Используя более эффективное ядро, лучшее прогнозирование направления переходов, расположенные на кристалле кэши большей емкости, больший размер строки кэша и аппаратную предварительную выборку, микропроцессор SPARC64-GP способен обеспечить высокую производительность на серверных приложениях, работающих с большими наборами данных и чисел с плавающей точкой.

Семейство корпоративных Unix-серверов GP7000F

На сегодняшний день Siemens - это одна из ведущих компаний в области организации корпоративных вычислений, Fujitsu - лидер на рынке микропроцессоров, а операционная система Solaris - одна из наиболее популярных и распространенных разновидностей Unix. Интеграция технологий и возможностей этих трех основных компаний позволила создать достаточно перспективное семейство серверов, поддерживающее более 15 тыс. приложений независимых разработчиков ПО.

Основные свойства семейства серверов GP7000F:

- наличие напольных и монтируемых в стойку систем (модели M200R, M400R, M600R);

- новые процессоры SPARC64-GP и высокоскоростная архитектура коммутации для построения симметричных мультипроцессорных систем;

- использование исправляющих одиночные ошибки кодов (ECC) на всех магистралях передачи данных, в основной памяти, а также в кэш-памяти первого и второго уровня;

- самотестирование системы при включении питания, а также автоматическая реконфигурация системы при отказах процессоров, компонентов памяти и шин PCI;

- средства управления системой, включающие интегрированные средства диагностики аппаратуры и наблюдения за ее состоянием;

- поддержка 16-разрядных интерфейсов Ultra SCSI;

- избыточные дисковые накопители, источники питания и вентиляторы - все с возможностью горячей замены.

Основные характеристики моделей M200, M400 и M600 представлены в таблице 2.

Кроме того, высшие модели семейства GP7000F (M800, M1000 и M2000) обладают следующими дополнительными возможностями (таблица 3):

- реализация концепции доменов (возможности распределения ресурсов и образования до 16 отдельных разделов);

- динамическая реконфигурация (изменение размеров разделов, добавление или удаление отдельных стоек, системных плат и т.д.);

- горячая замена процессоров, плат памяти и слотов PCI;

- коммутатор второго уровня для объединения процессоров, размещаемых в нескольких стойках;

- системная «шина» с контролем передачи данных (ECC);

- возможность одновременной работы печатных плат с различной тактовой частотой процессоров;

- дополнительная возможность установки средств дублирования и горячей замены платы управления системы (ее работа не зависит от состояния процессоров);

- дублирование схем ввода питающих напряжений переменного тока;

- пространство, обеспечивающее возможность установки до 30 устройств ввода/вывода в каждой 19-дюймовой стойке.

Особо следует отметить возможность использования всех симметричных мультипроцессоров семейства GP7000F в качестве узлов высокопроизводительных кластеров с повышенным коэффициентом готовности.

Серверы семейства GP7000F охватывают практически все возможные области применения на современном предприятии: от уровня филиала (M200), отдела (M400) и отделения (M600) для создания многопользовательских систем, обеспечивающих сервисы работы с файлами и печати, Internet-серверов, серверов приложений и баз данных, до уровня корпорации (M800, M1000, M2000) для реализации централизованных вычислений и крупных хранилищ данных в том числе и в кластерных конфигурациях.

Заключение

Несмотря на указанные в статье преимущества процессора SPARC64-GP его все-таки нельзя считать прямым конкурентом процессору UltraSPARC II - скорее они дополняют друг друга, причем первый более приспособлен для построения систем, реализующих критически важные решения. Прямыми конкурентами SPARC64-GP являются процессоры IBM Power3 и HP PA-8500, которые также обладают очень высокой производительностью при выполнении целочисленных операций и операций с плавающей точкой, а также лучше обрабатывают промахи кэш-памяти по сравнению с UltraSPARC II. Кроме того, они обеспечивают сравнимый уровень надежности вычислений, который ожидается от серверов для критически важных приложений современных корпораций. Ближайшие планы компании Sun Microsystems связаны с процессором UltraSPARC III, который по своим и скоростным возможностям заметно превосходит UltraSPARC II, исправляя, в частности, его слабые стороны. Таким образом, компании Fujitsu в секторе серверов для критически важных приложений придется конкурировать и с Sun.

Тем не менее, линия серверов Fujitsu GP7000F обладает прекрасными параметрами производительности, масштабируемости и надежности и может выдержать конкуренцию со стороны любого поставщика корпоративных серверов. Благодаря совместимости аппаратных и программных средств в эти серверы можно устанавливать и будущие процессоры UltraSPARC III. Правда, на этот счет у Fujitsu имеются свои планы. Помимо процессора SPARC64-GP, работающего на частоте 500 МГц, в середине 2001 года ожидается выход нового процессора с частотой 1 ГГц.

Об авторе

Виктор Шнитман — сотрудник Институту системного программирования РАН. С ним можно связаться по электронной почте по адресу: vzs@ispras.ru

| Свойства | SPARC64-GP | UltraSPARC II |

| SPECint95 | 17,6 | 16,1 |

| SPECfp95 | 26,6 | 23,5 |

| МГц | 272 | 360 |

| MFLOPS (пиковая) | 816 | 720 |

| Транзисторов | 17,6 млн. | 5,4 млн. |

| Размер кэш-памяти D1/I1;I0 | 64 Kбайт/64 Kбайт; 16 Kбайт | 16 Kбайт/16 Kбайт; 0 |

| Максимальный размер кэша L2 | 16 Мбайт | 16 Мбайт |

| Строка кэш-памяти | 64 байт | 32 байт |

| Пропускная способность шины данных к кэшу L2 | 4.3 Гбайт/с | 2,88 Гбайт/с |

| Размеры страниц | 4 Кбайт - 4 Гбайт | 8 Кбайт - 4 Мбайт |

| Неупорядоченное выполнение | Да | Нет |

| Аппаратные средства RAS | Четность, ECC | Меньше |